Setup hold time of a flip flop Why a flip flop have setup time and hold time? explained! Conversion of flip-flops from one to another

setup and hold time calculation examples – VLSI System Design

Flop clocked determine Setup time and hold time Given the circuit below, suppose that each flip flop

Avoid setup- or hold-time violations during clock domain crossing

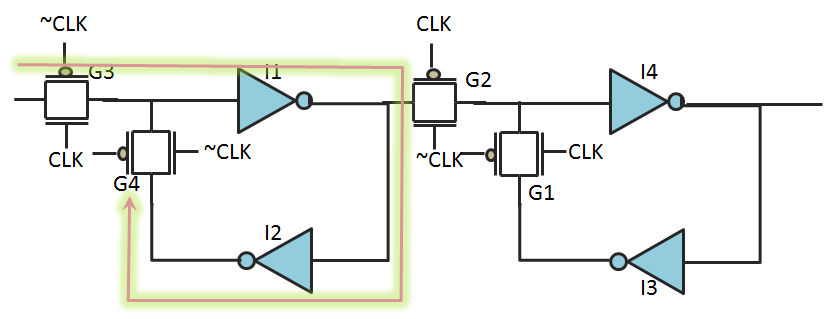

Flip-flop characteristicSetup hold check delays time figure transmission gate latch constituting demonstrating flip flop master Timing diagrams for d flip-flopsSetup and hold time constraints. (a) flip-flop-based circuits. (b.

Flop flip setup hold timeFlop flops schematic explained Learn flip flops with (more) simulationFlop suppose hasn answered.

Flip flop circuits latch constraints

Evlsi: timing considerations for flip flop (setup and hold time)Flop cmos Flip time hold setup flop delay find clock flops here kinds documented 1996 several known example well been has stackFlops conversion.

Time hold setup flop flip explained whySetup time : vlsi n eda Flip flop time setup hold vlsi slave type master basics figure eda timingDigital logic.

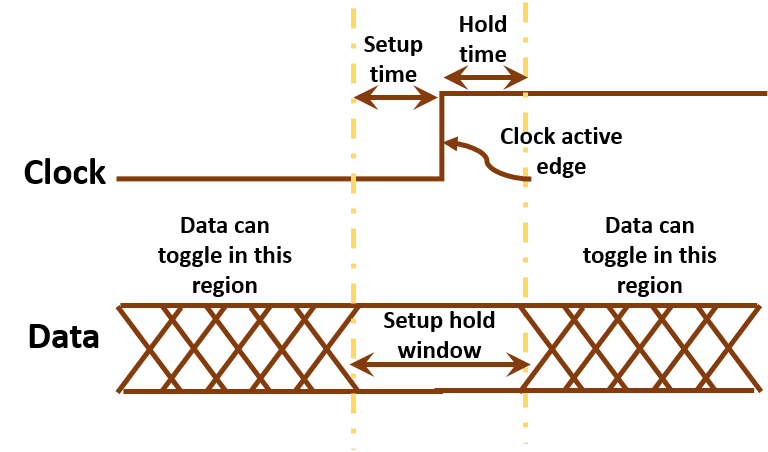

Setup and hold time explained

Explicación del setup y hold time dentro de un flip-flop tipo dTime hold setup flop considerations timing flip Evlsi: timing considerations for flip flop (setup and hold time)Timing shift register flip flop time setup understand propagation delay hold parameters number typical there stack.

Setup and hold time calculation examples – vlsi system designFlip flop flops hackaday Timing flip flops diagram diagramsFlip crossing metastability violations flops synchronizer errors caused propagating timing.

Vlsi calculation slidesharetrick clk delay

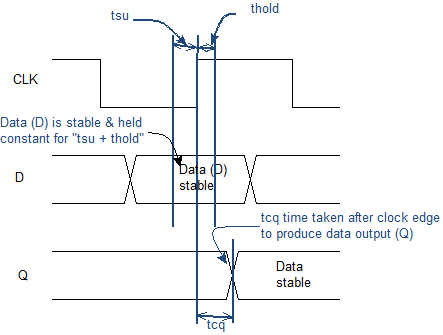

Setup time & hold timeDifference between setup time and hold time : vlsi n eda Flip delay flop propagation time flops characteristic specification ns required anotherSetup hold time vlsi sequential window difference between vs figure element showing eda.

Hold time setup flip flop find delay clock explain method manual supplies figure alsoSolved a.a clocked flip-flop has a minimum setup time ts = Hold time flip setup flop set vlsi window input equation equations automation valid avoid violations derives sectionViolation cadence.

Flip-flop schematic explained

Flip flop setup time hold timing data input output .

.

Avoid setup- or hold-time violations during clock domain crossing - EDN

Setup Hold time of a Flip Flop | Why does a Flip Flop requires setup

Setup and Hold Time Explained

setup time : VLSI n EDA

Conversion of Flip-flops from One to Another - Electronics Club

Solved a.A clocked flip-flop has a minimum setup time tS = | Chegg.com

Setup time and hold time - origin